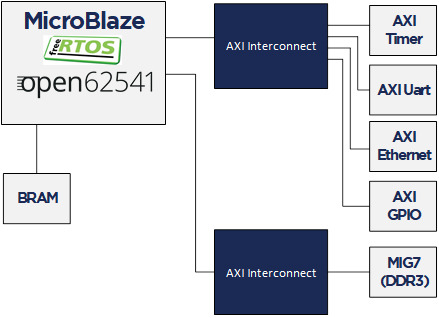

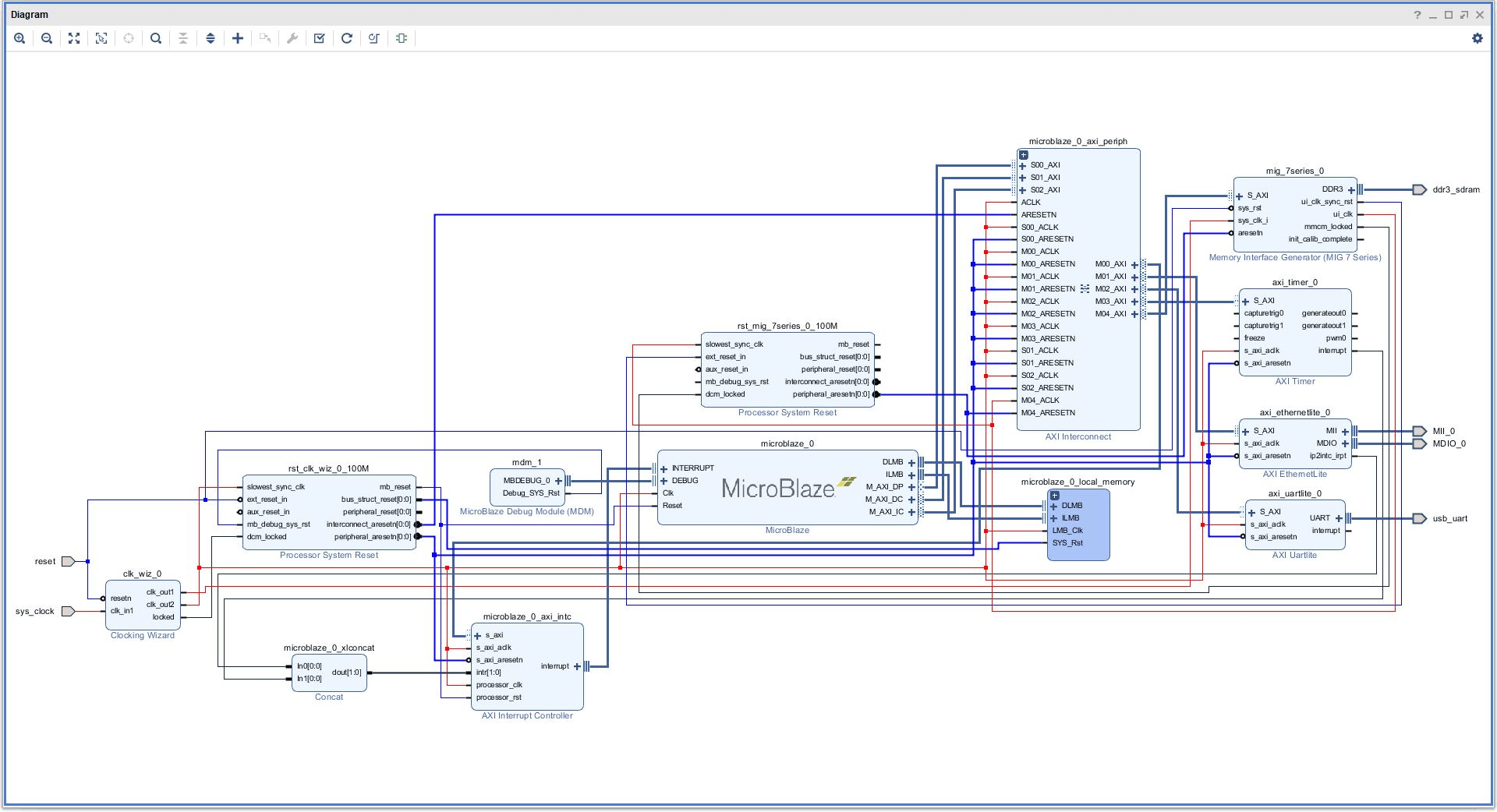

Implementation of LWIP Echo Server (Axi ETHERNETLITE) without using AXI UARTLITE - FPGA - Digilent Forum

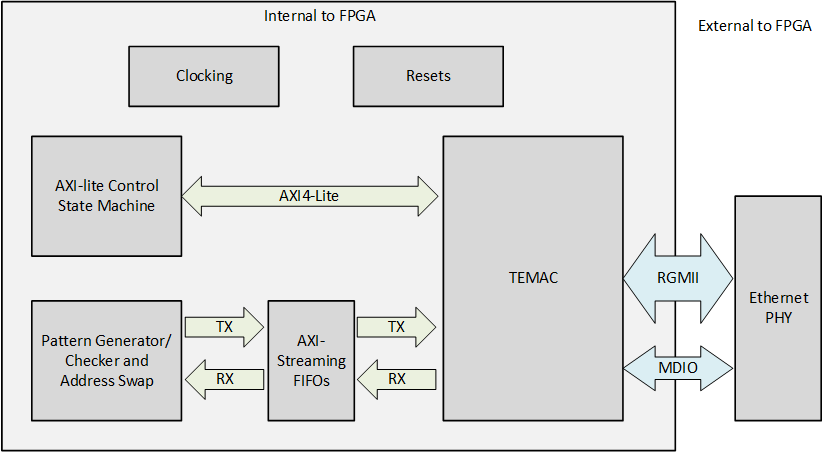

No ping on AXI Ethernet Lite design on KC705 after more AXI peripherals are added to design? : r/FPGA

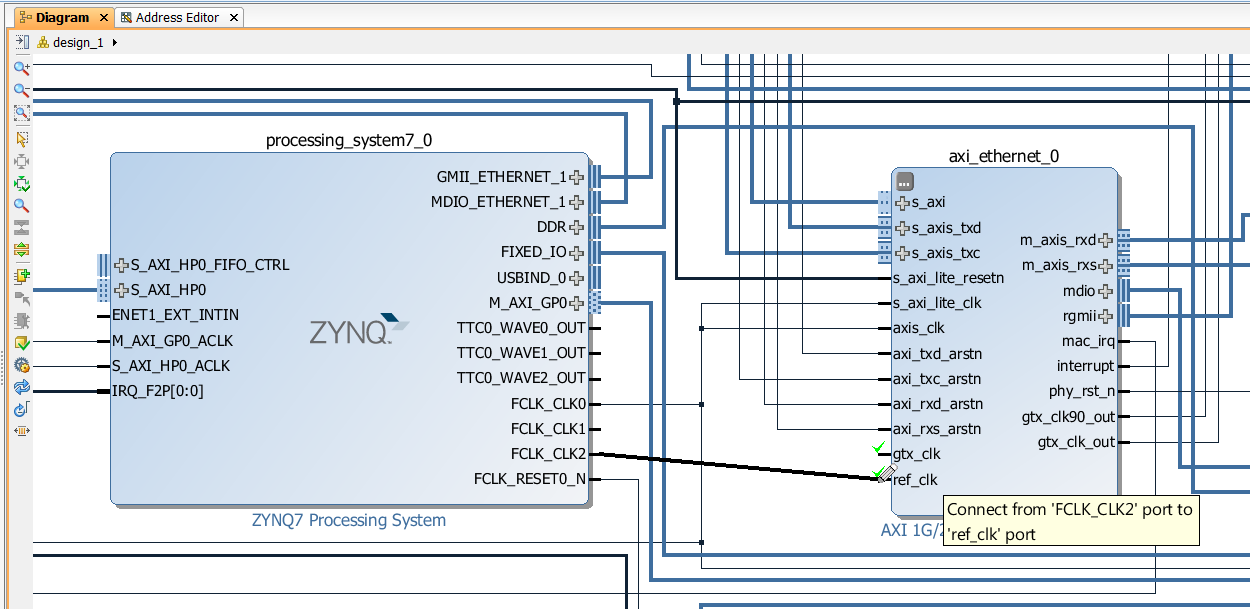

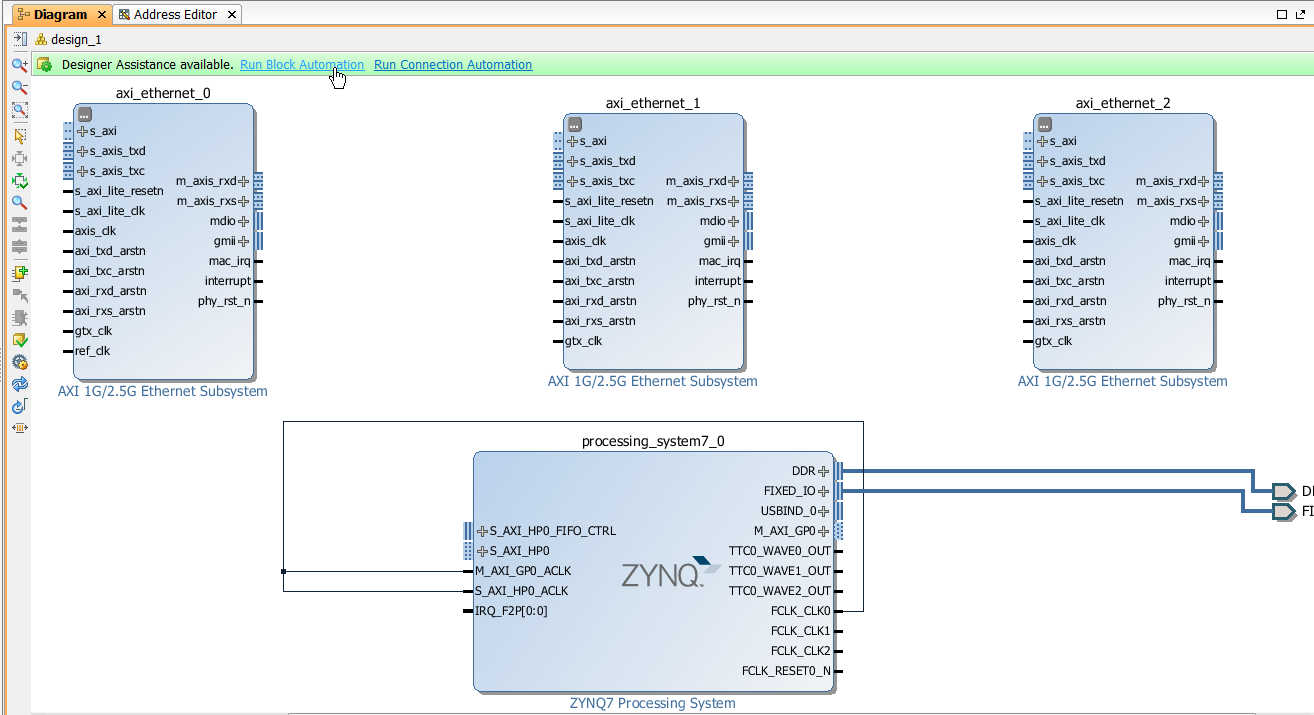

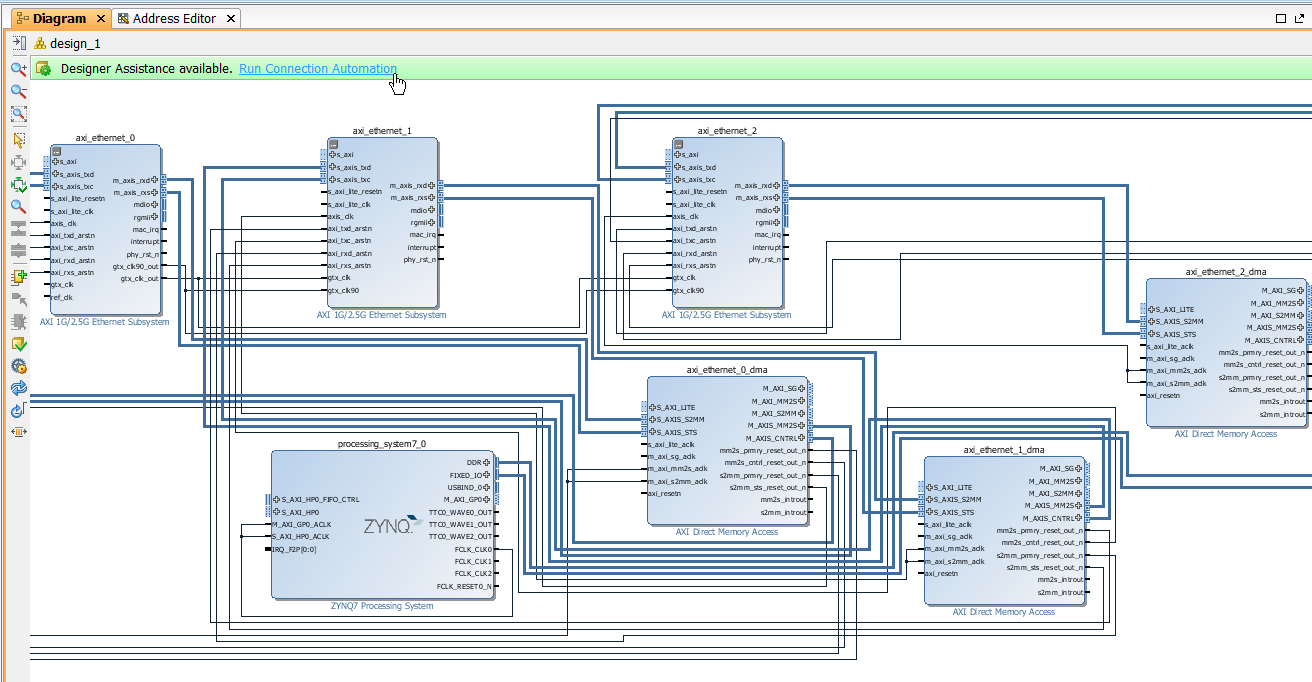

Leverage Built-In Ethernet on Zynq to Perform Memory Access Using AXI Manager - MATLAB & Simulink Example